#### **University of New Orleans**

## ScholarWorks@UNO

University of New Orleans Theses and Dissertations

**Dissertations and Theses**

Summer 8-13-2014

# Efficient FPGA Architectures for Separable Filters and Logarithmic Multipliers and Automation of Fish Feature Extraction Using Gabor Filters

Arjun Kumar Joginipelly arjunrao143@gmail.com

Follow this and additional works at: https://scholarworks.uno.edu/td

Part of the Digital Circuits Commons, Electrical and Electronics Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Joginipelly, Arjun Kumar, "Efficient FPGA Architectures for Separable Filters and Logarithmic Multipliers and Automation of Fish Feature Extraction Using Gabor Filters" (2014). *University of New Orleans Theses and Dissertations*. 1876.

https://scholarworks.uno.edu/td/1876

This Dissertation is protected by copyright and/or related rights. It has been brought to you by ScholarWorks@UNO with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/or on the work itself.

This Dissertation has been accepted for inclusion in University of New Orleans Theses and Dissertations by an authorized administrator of ScholarWorks@UNO. For more information, please contact scholarworks@uno.edu.

# Efficient FPGA Architectures for Separable Filters and Logarithmic Multipliers and

#### Automation of Fish Feature Extraction using Gabor Filters

#### A Dissertation

Submitted to the Graduate Faculty of the

University of New Orleans

in the partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in

Engineering and Applied Sciences

Electrical Engineering

by

Arjun Kumar Joginipelly

M.S. University of New Orleans, 2010

Aug 15 2014

© Copyright 2014 Arjun Kumar Joginipelly All rights reserved

### **Dedication**

I dedicate this work to my parents, Joginipelly Raj Gopal Rao and J. Prabha Rani; to my grandparents Potlapally Bapu Rao and P. Bharatamma; to my uncles, P. Govind Rao and P. Mohan Rao; to my sister and brother, M. Sri Laxmi and J. Anil Kumar. The blessings, unconditional love, and constant support you all gave were always with me and encouraged me in stepping forward in life.

#### Acknowledgments

First and above all, I praise God for giving me this opportunity and granting me the capability to proceed successfully in completing my dissertation overseas. This dissertation would not have been possible without the guidance and support of several individuals who in one way or other contributed and extended their valuable assistance in the completion of this study.

I would like to express enormous gratitude to Dr. Dimitrios Charalampidis, my advisor, for his help, suggestions, and guidance throughout the course of my dissertation. I appreciate his direction, supervision of my work, and his patience which helped me to progress in the right direction. I would like to thank Dr. George Ioup, Dr. Juliette Ioup, Dr. Huimin Chen and Dr. Vesselin Jilkov, for their willingness to serve as members of my dissertation committee.

Most importantly, I would like to thank my parents and grandparents, for teaching me that responsibility in life is to learn, to be happy, and to know and understand myself; only then I could understand and help others. I am indebted to them for encouraging me in all of my pursuits and inspiring me to follow my dreams. I always knew that you believed in me and wanted the best for me.

I acknowledge my friend Mr. Rajesh Chary, for his valuable help and support throughout my dissertation. His patience, assistance, and constructive criticism helped me in shaping my personal and academic life for complex situations. I would like to thank Patricia Robbert, for giving me the opportunity to work as a teaching assistant in Physics Department. This helped me in improving speaking and presentation abilities, and support myself financially for continuing my studies at University of New Orleans.

I would like to thank Jeevan Allagar, for his time and patience in helping me to understand the importance of moving forward in life taking both success and failures along side with me. Finally, I would like to thank Bing & Michael Simpson, Janu, Nag Bhai, and each and everyone, for listening, offering me advice and supporting me throughout my dissertation.

#### **List of Acronyms**

FPGA – Field Programmable Gate Arrays

NOAA – National Oceanic and Atmospheric Administration.

ASIC – Application Specific Integrated Circuit

RAM – Random Access Memory

HDL – Hardware Description Language

VHDL – Very High Speed Integrated Circuits HDL

DSP – Digital Signal Processor

2D – Two Dimensional

EMB – External Memory Bandwidth

CC – Clock Cycle

OCDB – On-chip Data Buffers

FB – Full Buffering

PB – Partial Buffering

MWPB - Multi-window Partial Buffering

LUT – Look-Up-Table

ICR – Intermediate Convolution Result

FCR – Final Convolution Result

FIFO – First-In-First-Out

BRAM - Block RAM

SDRAM – Synchronous Dynamic RAM

DDRAM – Double Data Rate RAM

MUX – Multiplexer

DEMUX – Demultiplexer

CSC - Central Selection Controller

VR – Vertical Results

HR – Horizontal Results

LNS – Logarithmic Number System

OD – Operand Decomposition

MSB – Most Significant Bit

MSE – Mean Square Error

IM – Iterative Mitchell

NCE – Non-Controlled Environments

SEFSC – Southeast Fisheries Science Center

EM – Epinephelus morio or red grouper

OC – Ocyurus chrysurus or yellow tail snapper

ABC – Allowable Biological Catch

GF – Gabor Filters

MA – Moving Average

## **Table of Contents**

| Li                       | st of l | Figures                                                              |                                                           | ix  |  |  |  |

|--------------------------|---------|----------------------------------------------------------------------|-----------------------------------------------------------|-----|--|--|--|

| Li                       | st of ' | <b>Tables</b>                                                        |                                                           | xi  |  |  |  |

| Al                       | ostrac  | et                                                                   |                                                           | xii |  |  |  |

| 1                        | Intr    | oductio                                                              | on                                                        | 1   |  |  |  |

|                          | 1.1     | Motiva                                                               | ation                                                     | 1   |  |  |  |

|                          | 1.2     | Disser                                                               | tation Outline                                            | 3   |  |  |  |

|                          | 1.3     | Disser                                                               | tation Contributions                                      | 4   |  |  |  |

| 2                        | Effic   | cient FI                                                             | PGA Implementation of Separable Convolution Architectures | 5   |  |  |  |

|                          | 2.1     | Abstra                                                               | nct                                                       | 5   |  |  |  |

|                          | 2.2     | Introd                                                               | uction                                                    | 5   |  |  |  |

|                          | 2.3     | Review                                                               | w of Separable Convolution Methods                        | 8   |  |  |  |

|                          |         | 2.3.1                                                                | FB Scheme for Separable Convolution                       | 8   |  |  |  |

|                          |         | 2.3.2                                                                | PB Scheme for Separable Convolution                       | 9   |  |  |  |

|                          | 2.4     | Propos                                                               | sed Separable Convolution Scheme and Implementation       | 11  |  |  |  |

|                          |         | 2.4.1                                                                | Shift Register Modules                                    | 11  |  |  |  |

|                          |         | 2.4.2                                                                | Multiplexer and Demultiplexer Modules                     | 12  |  |  |  |

|                          |         | 2.4.3                                                                | Multipliers and Adder                                     | 13  |  |  |  |

|                          |         | 2.4.4                                                                | Central Selection Controller                              | 13  |  |  |  |

| 2.5 Performance Analysis |         | Perfor                                                               | mance Analysis                                            | 14  |  |  |  |

|                          | 2.6     | Conclu                                                               | usions                                                    | 17  |  |  |  |

| 3                        | An l    | An Efficient Method of Error Reduction in Logarithmic Multiplication |                                                           |     |  |  |  |

|                          | for l   | Filterin                                                             | g Applications                                            | 18  |  |  |  |

|                          | 3.1     | Abstra                                                               | nct                                                       | 18  |  |  |  |

|                          | 3.2     | Introd                                                               | uction                                                    | 18  |  |  |  |

|                          | 3.3     | Reviev                                                               | w of Logarithmic Multipliers                              | 21  |  |  |  |

|    |        | 3.3.1    | Mitchell Logarithmic Multiplier                          | 21 |

|----|--------|----------|----------------------------------------------------------|----|

|    |        | 3.3.2    | Derivation of IM log multiplier                          | 23 |

|    | 3.4    | Propos   | sed logarithmic multiplier                               | 25 |

|    | 3.5    | Results  | s and Discussion                                         | 26 |

|    | 3.6    | Extens   | ion of Proposed Logarithmic Multiplier                   | 29 |

|    | 3.7    | Conclu   | asions                                                   | 33 |

| 4  | Spec   | cies-Spe | ecific Fish Feature Extraction Using Gabor Filters       | 34 |

|    | 4.1    | Abstra   | ct                                                       | 34 |

|    | 4.2    | Backgr   | round                                                    | 34 |

|    | 4.3    | Gabor    | Filters Used For Fish Feature Extraction                 | 36 |

|    |        | 4.3.1    | Epinephelus morio Feature Extraction Using Gabor Filters | 38 |

|    |        | 4.3.2    | Ocyurus chrysurus Feature Extraction Using Gabor Filters | 39 |

|    | 4.4    | Results  | s and Discussion                                         | 41 |

|    | 4.5    | Conclu   | asions                                                   | 47 |

| 5  | Con    | clusions | s and Future Work                                        | 48 |

|    | 5.1    | Conclu   | isions                                                   | 48 |

|    | 5.2    | Future   | Work                                                     | 49 |

| Bi | bliogı | caphy .  |                                                          | 49 |

| Aŗ | pend   | ices     |                                                          | 55 |

|    | VHI    | DL Sour  | ce Codes                                                 | 55 |

|    | Matl   | ab Sour  | rce codes                                                | 60 |

| Vi | ta .   |          |                                                          | 68 |

# **List of Figures**

| Fig. 2.1: | Illustration of available common rows for consecutive convolution win-             |    |

|-----------|------------------------------------------------------------------------------------|----|

|           | dows $W_1$ , $W_2$ and $W_K$                                                       | 6  |

| Fig. 2.2: | FB scheme for separable convolution                                                | 9  |

| Fig. 2.3: | PB scheme for separable convolution                                                | 9  |

| Fig. 2.4: | Proposed FPGA architecture for a kernel of size $3 \times 3$                       | 10 |

| Fig. 2.5: | Order in which the image pixels are read                                           | 12 |

| Fig. 2.6: | Central selection controller timing diagram                                        | 14 |

| Fig. 2.7: | FB, PB and proposed schemes power consumption (mW) for a $3\times3$ filter         | 15 |

| Fig. 2.8: | Comparison between FB, PB and proposed schemes for various filter                  |    |

|           | sizes in terms of flip flops shown using barplots                                  | 16 |

| Fig. 2.9: | Comparison between FB, PB and Proposed schemes for various filter                  |    |

|           | sizes in terms of LUTs shown using barplots                                        | 16 |

| Fig. 3.1: | Actual values and Mitchell's approximated values of $log_2(N)$                     | 22 |

| Fig. 3.2: | MSE between the Mitchell, OD, IM and proposed methods using input                  |    |

|           | signals of size $1\times256$ and Gaussian filter of size $1\times13$ , shown with  |    |

|           | barplots                                                                           | 28 |

| Fig. 3.3: | MSE between the Mitchell and the proposed method extension for                     |    |

|           | Mitchell using input signals of size $1\times256$ and Gaussian filter of size      |    |

|           | $1 \times 13$ , shown using barplots                                               | 31 |

| Fig. 3.4: | MSE between the OD and the proposed method extension for OD using                  |    |

|           | input signals of size $1\times256$ and Gaussian filter of size $1\times13$ , shown |    |

|           | using barplots                                                                     | 31 |

| Fig. 3.5: | MSE between IM and the proposed method extension for IM using input                |    |

|           | signals of size $1\times256$ and Gaussian filter of size $1\times13,$ shown using  |    |

|           | barplots                                                                           | 32 |

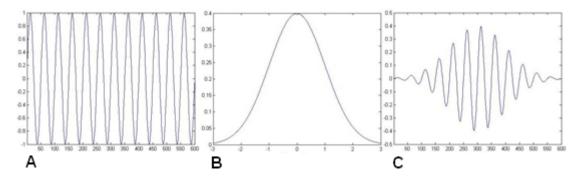

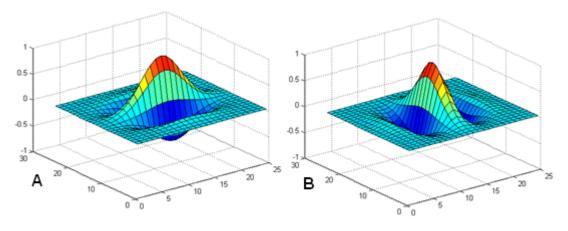

| Fig. 4.1:  | 1D Gabor filter                                                           | 37 |

|------------|---------------------------------------------------------------------------|----|

| Fig. 4.2:  | 2D Gabor filters with $\sigma_x^2 = \sigma_y^2 = 4$                       | 37 |

| Fig. 4.3:  | EM pre-processing steps                                                   | 39 |

| Fig. 4.4:  | Filtering results of horizontal and vertical Gabor filters on EM          | 39 |

| Fig. 4.5:  | EM tail band detection – maximum value per column $m_{I_r}^{EM}(x)$       | 39 |

| Fig. 4.6:  | OC pre-processing steps                                                   | 40 |

| Fig. 4.7:  | Filtering results of horizontal and vertical Gabor filters on OC          | 40 |

| Fig. 4.8:  | OC straight line detection – maximum value per row $m_{I_r}^{OC}(y)$      | 41 |

| Fig. 4.9:  | OC straight line detection when the fish is oriented at a different angle |    |

|            | with respect to $x$ axis                                                  | 42 |

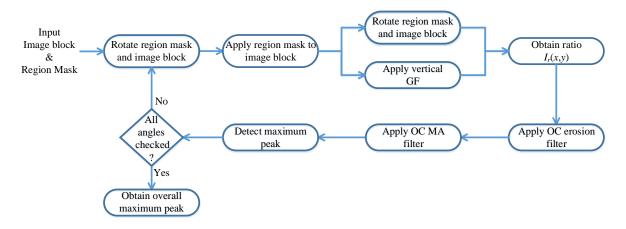

| Fig. 4.10: | Proposed algorithm flowchart                                              | 43 |

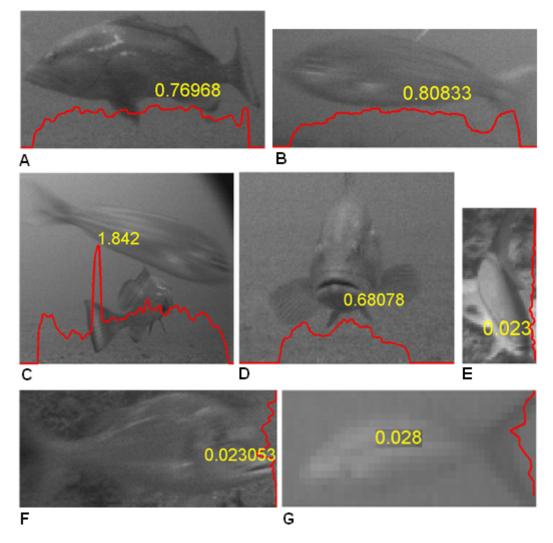

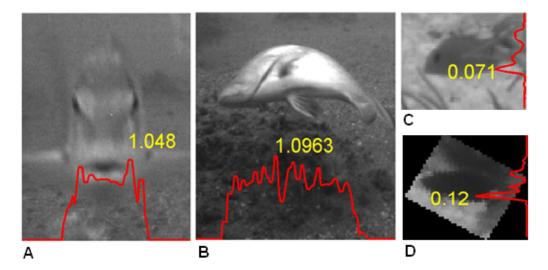

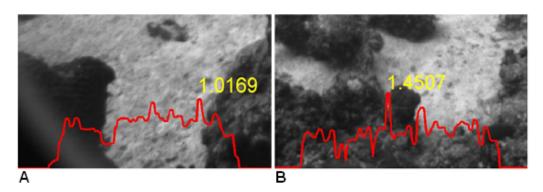

| Fig. 4.11: | Illustration of some EM and OC results                                    | 45 |

| Fig. 4.12: | Illustration of few cases of false alarms (non-EM detected as EM, or      |    |

|            | non-OC detected as OC)                                                    | 46 |

| Fig. 4.13: | Illustration of few cases of false alarms (non-fish detected as EM or OC) | 46 |

| Fig. 4.14: | Illustration of few cases where EM and OC are not detected by the         |    |

|            | algorithm.                                                                | 46 |

# **List of Tables**

| Table 2.1: | Characteristics of the three schemes for a $K \times K$ filter                | 14 |

|------------|-------------------------------------------------------------------------------|----|

| Table 2.2: | Comparison between FB, PB and proposed schemes for various filter             |    |

|            | sizes in terms of flip flops and LUTs using xilinx virtex 5 FPGA device $$ .  | 16 |

| Table 3.1: | MSE between the Mitchell, OD, IM and proposed methods using input             |    |

|            | signals of size $1\times 256$ and Gaussian filter of size $1\times 13$        | 27 |

| Table 3.2: | Resource utilization of non-pipelined logarithmic multiplier using the        |    |

|            | Mitchell, OD, IM (1, 2, 3 and 4 stages), and proposed method                  | 28 |

| Table 3.3: | MSE between the Mitchell, proposed method extension for Mitchell, OD,         |    |

|            | and proposed method extension for OD using input signals of size $1\times256$ |    |

|            | and Gaussian filter of size $1 \times 13$                                     | 30 |

| Table 3.4: | MSE between IM and the proposed method extension for IM using input           |    |

|            | signals of size $1 \times 256$ and Gaussian filter of size $1 \times 13$      | 32 |

| Table 4.1: | Information about reef fish images obtained from SEFSC Pascagoula             |    |

|            | laboratory                                                                    | 41 |

| Table 4.2: | EM results                                                                    | 43 |

| Table 4.3: | OC results                                                                    | 44 |

#### **Abstract**

Convolution and multiplication operations in the filtering process can be optimized by minimizing the resource utilization using Field Programmable Gate Arrays (FPGA) and separable filter kernels. An FPGA architecture for separable convolution is proposed to achieve reduction of on-chip resource utilization and external memory bandwidth for a given processing rate of the convolution unit.

Multiplication in integer number system can be optimized in terms of resources, operation time and power consumption by converting to logarithmic domain. To achieve this, a method altering the filter weights is proposed and implemented for error reduction. The results obtained depict significant error reduction when compared to existing methods, thereby optimizing the multiplication in terms of the above mentioned metrics.

Underwater video and still images are used by many programs within National Oceanic Atmospheric and Administration (NOAA) fisheries with the objective of identifying, classifying and quantifying living marine resources. They use underwater cameras to get video recording data for manual analysis. This process of manual analysis is labour intensive, time consuming and error prone. An efficient solution for this problem is proposed which uses Gabor filters for feature extraction. The proposed method is implemented to identify two species of fish namely Epinephelus morio and Ocyurus chrysurus. The results show higher rate of detection with minimal rate of false alarms.

#### Keywords

Separable Convolution, Image Processing, Field Programmable Gate Array (FPGA), Logarithmic Multipliers, Gabor Filters, Automated Fish Classification and Feature Extraction.

#### Chapter 1

#### Introduction

#### 1.1 Motivation

Embedded systems play an important role in digital image, video and signal processing with applications in wide areas such as digital cameras, traffic light controller systems [1], lane detection [2], medical devices, etc. In order to optimize the system performance to meet the ever increasing demand for efficient system performance, major metrics in terms of cost, resources, operation time, power consumption, resolution, and robustness are to be improved. Image processing systems which constantly demand for real-time processing power require new design methodologies and hardware accelerator architectures for hardware implementation.

In earlier times, image processing systems were mostly built with Application Specific Integrated Circuits (ASICs) which are not re-programmable (or re-configurable). A malfunction in one ASIC often results in a complete replacement of the faulty component. The ASIC's lack of flexibility to be reprogrammed is promoting their counterpart, namely the Field Programmable Gate Array (FPGA) chips.

FPGA's generally consist of a logic block-based system, which usually includes look-up-tables (LUT), flip-flops and some amount of random access memory (RAM), all wired together using a vast array of interconnects. All of the logic in an FPGA can be reconfigured with a different design as often as the designer likes. FPGAs can be configured by hardware engineers using a Hardware Design Language (HDL). The two principal languages which allows designers to design at various levels of abstraction are Verilog HDL (Verilog) and Very High Speed Integrated Circuits HDL (VHDL).

FPGAs can be developed to implement hardware design techniques such as parallelism and pipelining, which is not possible in dedicated Digital Signal Processing (DSP) designs. DSPs are a class of hardware devices that fall somewhere between an ASIC and a PC in terms of the

performance and the design complexity. ASICs were traditionally preferred over FPGAs because of their speed, lower power consumption, and higher functionality. However, the improvement on FPGA technology in recent years closed this gap. ASIC design methods can also be used for FPGA design, facilitating gate level implementations, thereby decreasing development time and time-to-market. However, engineers usually use a hardware language, which allows for a design methodology similar to software design. Maintenance can be performed when an error is found in the implemented design, since the FPGA fabric can always be reconfigured. This software view of hardware design allows for a lower overall support requirements, lower cost, and design abstraction. The key advantages of FPGAs when compared to DSP implementations include performance, integration and customization using parallel and pipeline design techniques. Due to the support of parallelism, FPGAs may be able to achieve huge gains in performance compared to DSP implementations.

A thorough study on the capabilities of the FPGAs provided the motivation to utilize its features for implementing image processing algorithms [3] with an aim of minimizing time-to-market cost, enabling rapid prototyping of complex algorithms and finally simplifying the tedious process of debugging and verification. Some works of image processing applications using FPGAs have been reported such as edge detection [2], enhancement [4], and smoothing [5], convolution form the basic component. For instance, for image size of  $256 \times 256$  with number of frames = 25/sec and kernel size of  $3 \times 3$ , real time image convolution requires 589,824 multiplications and 524,288 additions. Furthermore, as the image resolution and refresh rate increases, computational requirements of the convolution unit significantly increases. Hence, due to high performance requirements, FPGAs are an ideal choice for implementation of real time image processing algorithms. Given the importance of digital image processing and the significance of their implementations on hardware to achieve better performance, this dissertation addresses efficient architectures of separable convolution and logarithmic multiplication on FPGA using VHDL language.

"A picture is worth a thousand words." As human beings, we can extract information from a picture based on what we see and our background knowledge. Based on this analogy, we can train computers by building models to extract efficient visual features [6] from an image or video

sequence. Hence, feature extraction is the fundamental step in any automated image analyzing system which is widely used in one of the areas of identifying and quantifying living marine resources.

Species detection is necessary to explore new species and their richness in any ecology. Many fisheries use manual accumulation and analyze large amounts of data obtained using underwater cameras for recognition and classification of species. This tedious process is easily prone to errors as it involves manual analysis. This provided the motivation to the proposed method on species-specific feature extraction using Gabor filters for extracting two species of fish namely Epinephelus Morio, and Ocyurus Chrysurus. The proposed method gave the desired results with a significant identification rate and negligible false alarms.

#### 1.2 Dissertation Outline

The rest of the dissertation is organized as follows: Each chapter is allocated for a specific methodology explaining the contribution of dissertation work in improving on the existing methodologies.

Chapter 2 covers the convolution operation in detail and its functioning in filters and explains the need for optimizing in terms of resource utilization and external memory bandwidth. It then follows up with a thorough review on various existing FPGA separable convolution methods. The proposed FPGA architecture with separable filter kernels, its implementation, and the results are then presented.

Chapter 3 covers the multiplication operation in filters addressing the questions such as how its optimization can improve the filter performance in terms of metrics such as power consumption, operation time and resource utilization. One of the ways to achieve this is to convert integer multiplication to logarithmic multiplication. Various existing methods on logarithmic multipliers are then reviewed following up with the proposed method. The main objective of this method is to reduce the multiplication error by altering the filter weights.

Chapter 4 covers the proposed method to improve on manual fish feature extraction process currently in use by National Oceanic Atmospheric Administration (NOAA) fisheries group. An

in depth need for the automation of the feature extraction and species classification process is explained. One of the solution is to use Gabor filters for feature extraction. The proposed algorithm using Gabor filter is implemented and the results obtained are then presented which show prominent success rate.

Chapter 5 gives the overall conclusions drawn from all the proposed methods and discusses on how they can be improved further in future.

#### 1.3 Dissertation Contributions

In this dissertation, issues related to convolution and multiplication on FPGA hardware are resolved in an efficient way. With a major concern given to address external memory bandwidth, on-chip data buffers and power consumption which are common to most imaging applications. Architectural considerations as well as design methodology constitute the main scope of the dissertation research work. Efficient FPGA architectures are presented for separable convolution which provide a good balance between on-chip resource utilization and external memory bandwidth. An efficient logarithmic multiplier based on Mitchell [7] is proposed and implemented on FPGA. Automation of fish feature extraction using Gabor filters is proposed as an efficient solution to manual fish analysis problem. The list of publications which are accepted or currently in the process of submission from this dissertation research are as follows:

- 1. Arjun Kumar Joginipelly, Dimitrios Charalampidis, "Efficient Separable Convolution Using FPGA's", currently in the process of submission. [Chapter 2].

- 2. Arjun Kumar Joginipelly, Dimitrios Charalampidis, "Efficient Mitchell-based Logarithmic Multiplier", currently in the process of submission. [Chapter 3]

- Arjun Kumar Joginipelly, Dimitrios Charalampidis, George Ioup, Juliette Ioup, Charles H

Thompson, "Species-Specific Fish Feature Extraction Using Gabor Filters", proceedings

of 66<sup>th</sup> Gulf and Carribbean Fisheries Institute, Corpus Christi, Texas, USA, Nov 2013.

[Chapter 4]

#### Chapter 2

#### **Efficient FPGA Implementation of Separable Convolution Architectures**

#### 2.1 Abstract

Two-dimensional (2D) convolution is an essential component of several image and video processing applications. In general, the convolution operation is computationally expensive. Field Programmable Gate Array (FPGA) architectures have been used to mitigate this problem owing to their parallel processing capabilities. Using separable filter kernels can further improve the convolution operation both in terms of resource utilization and speed. However, although several 2D convolution implementations have been presented in the literature, research on separable convolution using FPGA is limited. In this chapter, a new separable FPGA-based convolution architecture is proposed. The goal is to reduce both on-chip resource utilization and external memory bandwidth for a given processing rate of the convolution unit. Comparisons with existing separable convolution methods demonstrate the achievement of the stated goal.

#### 2.2 Introduction

Two dimensional (2D) convolution is widely used in image processing applications such as edge detection [2], enhancement [4], and smoothing [5]. Spatial domain convolution using a kernel of size  $K \times K$  requires  $K^2$  multiplications and  $(K^2 - 1)$  additions per pixel. The convolution output at image location (x, y) can be computed as the sum of products between kernel weights and corresponding pixel values located within the  $K \times K$  image window centered at (x, y).

Real-time hardware-based convolvers require a large amount of resources including adder circuits, multipliers or multiplier-equivalent circuits, and internal and/or external memory. Major considerations include the external memory bandwidth (EMB), namely the number of pixels read from external memory or device per clock cycle (cc), the amount of on-chip data buffers (OCDB) where input or processed data is stored, and the amount of multiplier-related resources. Several schemes [8],[9],[10],[11] proposed in the literature address EMB and OCDB utilization.

In [8], a full buffering (FB) scheme was used for implementing 2D convolution. Delay line buffers were used to hold (K-1) rows of the input image. A partial buffering (PB) scheme was proposed in [9] to eliminate the line buffers by storing only small image portions in internal memory. However, achieving this goal resulted in an increased EMB. A multi-window PB (MWPB) scheme was proposed in [10] to overcome the problems in FB and PB schemes.

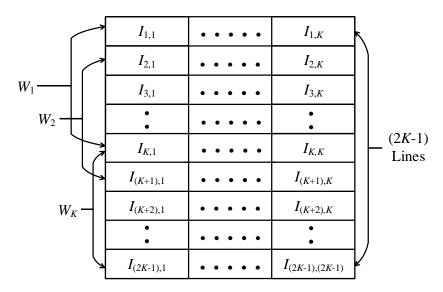

Similarly to PB, the MWPB scheme aimed at storing only small portions of the image data in internal memory. The main objective, however, was to reuse the common data shared by consecutive windows to the full extent possible. Therefore, the same image data did not have to be read K times as in the case of PB. This concept is illustrated in Fig. 2.1. Since K windows of size  $K \times K$  ( $W_k$ , k = 1, ..., K) are available in (2K - 1) consecutive image rows, K filter outputs can be produced by processing (2K - 1) rows. Thus, each pixel is read only (2K - 1)/K times, or practically, two times.

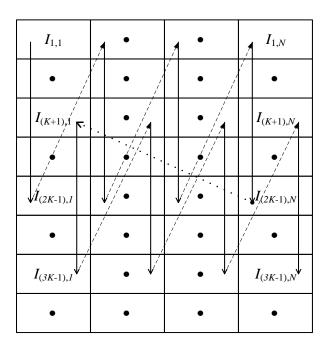

Figure 2.1: Illustration of available common rows for consecutive convolution windows  $W_1$ ,  $W_2$  and  $W_K$ .

The resources required for 2D convolution can be reduced by employing filters with separable kernels. A  $K \times K$  separable kernel can be decomposed into a horizontal  $1 \times K$  kernel and a vertical  $K \times 1$  kernel, so that only 2K multiplications and (2K-2) additions are required per pixel. Although several hardware-based 2D convolution implementations have been investigated, there is limited work on separable convolution using FPGA or VLSI architectures. In [5], steerable filters [12] were implemented using a separable filter component. In [13], an image

scaling architecture using separable filters was proposed. In [14], a separable implementation of Voltera filters was presented. In [15], singular value decomposition was used to approximate 2D filters as a cascade of separable and non-separable filters employing, respectively, embedded multipliers and reduced complexity LUT-based multipliers. In [16], FB-based separable convolution architectures and overlapping kernel techniques were investigated. Transform-based techniques were proposed [17] to perform 2D convolution in a separable manner.

Most existing works, including the ones mentioned above, mainly employ FB separable convolution schemes. Other works do not focus on separable convolution but only use it as one of the system components. Although FB schemes offer advantages with respect to non-separable techniques [16], they still require a large amount of resources due to line buffering. This chapter proposes an architecture that reduces both EMB and on-chip resource utilization for a given processing rate of the convolution unit. Section 2.4 presents the technical details of the proposed scheme.

Although it is not the objective of this work, employing LUT-based multiplier-equivalent circuits may further reduce resource utilization. Examples include log2 and inverse log2 modules [18], shift and accumulation block modules [19], optimized codes such as distributed arithmetic, output product coding, canonic signed digit coding, and binary sub-expression coding [20],[21], and common sub-expression elimination methods to replace constant multiplications with a network of adders and shifters [22]. Moreover, although the proposed work deals with linear convolution, cyclic convolution techniques have also been investigated in [23],[24].

This chapter is organized as follows: Section 2.3 discusses two separable convolution architectures. The first has been previously introduced in the literature [5],[14],[15],[25] and is based on the FB scheme. The second was implemented by the authors by modifying the PB scheme originally designed for non-separable convolution [9]. Section 2.4 introduces the proposed FPGA architecture. Section 2.5 presents performance analysis, and comparisons among the three architectures. Concluding remarks are presented in section 2.6.

#### 2.3 Review of Separable Convolution Methods

This section discusses separable convolution architectures based on the FB and PB schemes. The FB separable convolution scheme has been previously introduced in the literature [5],[15],[14],[25]. The PB separable convolution architecture is designed in this work as a straightforward modification of the non-separable PB-based scheme. In what follows, parameter P describes the image pixel depth, which for grayscale images is equal to 8 bits. Moreover, the expression "shift register array of size R" implies a total of P shift registers, each consisting of R flip flops.

#### 2.3.1 FB Scheme for Separable Convolution

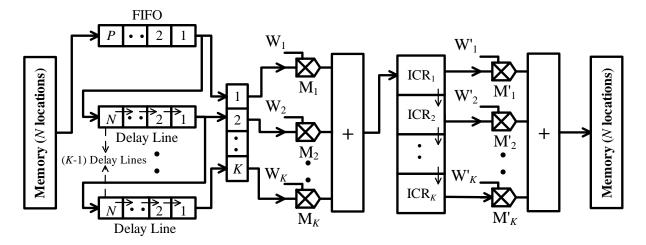

In [5],[25], an FB scheme was used to implement separable convolution. A similar architecture was presented in [14],[15]. The FB separable convolution scheme is depicted in Fig. 2.2. In summary, input pixels are read from external memory, one at a time, in a row-wise manner. Pixels are pushed into internal line buffers until (K-1) image rows, each consisting of N pixels, are read. Each time a new pixel from the K-th row is read and stored in FIFO, a total of K pixels, forming a vertical  $K \times 1$  window, are available and stored in K internal buffers. The products between the K pixels and the corresponding K vertical filter weights are obtained and summed together to produce the vertical intermediate convolution result (ICR). As pixels from the K-th row continue to be read, consecutive ICRs are stored in a shift register array of size K. The K ICRs are multiplied with the corresponding K horizontal filter weights and the results are summed together to obtain the final convolution result (FCR). The above process is repeated for all image pixels. Equivalently, the horizontal operation may be performed first followed by the vertical operation.

In a pipelined version of the FB scheme, one pixel is read and one FCR is produced per clock cycle, while a total of 2K multipliers should be available. Alternatively, in a non-pipelined version, the horizontal and vertical filters may share the same K multipliers. In this case, multiplexing is needed in order to select the appropriate inputs to the multipliers, namely vertical versus horizontal filter weights, and input data versus ICRs. In this case, one input pixel is read and one FCR is produced per two clock cycles. The advantage of the FB scheme is that

Figure 2.2: FB scheme for separable convolution

each pixel is read only once from external memory. Therefore, EMB equals only 1 or 0.5 pixels/cc using, respectively, the pipelined and non-pipelined versions of the scheme. The major disadvantage of this scheme is that shift register arrays of total size [(K-1)N+K+1)] are used for buffering, which accounts for a substantial percentage of FPGA resources. The problem becomes significant for large input image and kernel sizes.

Figure 2.3: PB scheme for separable convolution

#### 2.3.2 PB Scheme for Separable Convolution

The original PB scheme was developed for non-separable kernels [9] and is not presented here. Instead, a separable version of the PB scheme has been designed in this work, for the purpose of comparing with the FB separable convolution and the proposed schemes. In the separable

version of the PB scheme, presented in Fig. 2.3, K pixels located in a window of size  $K \times 1$  are read from external memory simultaneously and pushed in first-in-first-out (FIFO) blocks. The FIFO data are multiplied with the corresponding K vertical filter weights to produce the ICR. Similarly to the FB scheme, once K consecutive ICRs become available, they are multiplied with the corresponding K horizontal filter weights. The products are summed together to obtain the FCR. The process is repeated for all image pixels. Similarly to the FB scheme, a pipelined and a non-pipelined version may be considered.

The advantage of the PB separable convolution architecture is that only 2K data points has to be stored in internal buffers and shift register arrays. Therefore, the internal storage-related resources are reduced dramatically with respect to the FB scheme. However, each pixel is read K times from external memory resulting in a high EMB. The EMB equals K or K/2 pixels/cc using, respectively, the pipelined and non-pipelined versions of the scheme.

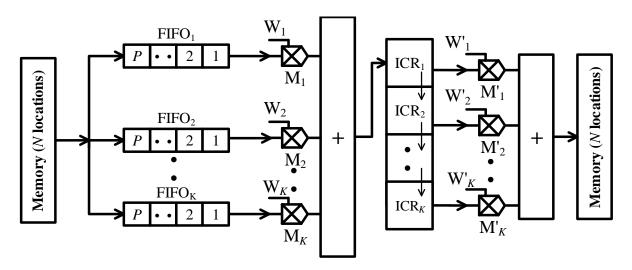

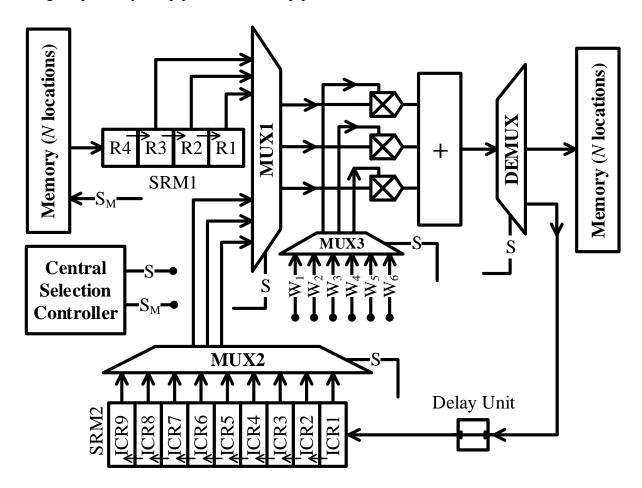

Figure 2.4: Proposed FPGA architecture for a kernel of size  $3 \times 3$

#### 2.4 Proposed Separable Convolution Scheme and Implementation

The objective of the proposed separable convolution technique is to reduce EMB, by reusing common data shared by consecutive processing windows, and OCDB, by eliminating line buffers. In this section, each module in the proposed separable convolution scheme is described in detail with reference to the FPGA implementation. The input image pixels are read from block RAM (BRAM), although other external memory elements such as synchronous dynamic RAM (SDRAM) or double date rate RAM (DDRAM) may also be used. Moreover, the implementation described next is what was referred earlier as the non-pipelined version, in which the same set of multipliers is shared by both vertical and horizontal 1D filters. The FPGA architecture of the proposed scheme with detailed schematic considering a kernel of size  $3 \times 3$  is shown in Fig. 2.4.

#### 2.4.1 Shift Register Modules

As described in the introduction and Fig. 2.1, EMB is reduced if information from (2K-1) rows is processed at a time. For this reason, pixels located in a  $(2K-1) \times 1$  window,  $W_A^{i,j}$ , are read one at a time before moving on to the next window. The superscript i,j indicates, respectively, the row and column position of the top pixel in  $W_A^{i,j}$ . In particular, the next window is  $W_A^{i,j+1}$ , if j=1,...,N-1 or  $W_A^{(i+K,1)}$  if j=N, in which case the current window  $W_A^{i,N}$  is located at the rightmost image column. The order in which pixels are read from the input image is presented in Fig. 2.5. In the proposed architecture, it is not necessary to store all 2K-1 rows of  $W_A^{i,j}$  as in the case of the MWPB scheme. Only K pixels located within a  $K \times 1$  subwindow, namely  $W_k$ , are needed at a time to produce a vertical convolution result. An additional pixel is read to be made available for processing the next subwindow  $W_{k+1}$ . Module SRM1, which consists of a shift register array of size (K+1), is used to hold and shift the input image pixels.

Each  $(2K-1) \times 1$  window provides K ICRs corresponding to K image subwindows  $W_k, k = 1, ..., K$  (see Fig. 2.1) within the same window  $W_A^{i,j}$ . Once K consecutive  $W_A^{i,j}$  windows are processed, a total of  $K^2$  ICRs are produced. These results are stored in a second shift register array of size  $K^2$  denoted as SRM2. For every new  $K \times 1$  image window, K new ICRs are shifted in SRM2, one at a time, while the K oldest ICRs are shifted out of SRM2.

As opposed to the scan method presented here, [26] requires that a  $(2K - 1) \times (2K - 1)$  image block is stored at a time, and mainly concentrates on how a single window is processed. However, it does not describe how processing should transition from one window to the next. Due to this uncertainty, [26] is not compared to the proposed work.

#### 2.4.2 Multiplexer and Demultiplexer Modules

The proposed architecture utilizes three multiplexers (MUX1, MUX2, MUX3) and one demultiplexer (DEMUX) modules. In particular, MUX1 selects pixels from either SRM1 or SRM2, depending on the selection signal S generated from the central selection controller (CSC). If S = HIGH then MUX1 selects pixels from SRM1. In this case, the multiplier and adder modules generate ICRs which are stored temporarily to SRM2 through DEMUX. When SRM2 is completely filled, S is set to LOW by the CSC, and MUX2 assigns K out of  $K^2$  ICRs to MUX1. In this case, the multiplier and adder modules generate the FCRs. DEMUX sends the FCRs in another BRAM or other memory. It should be mentioned that ICRs are fed back to SRM2 from DEMUX with a 3-clock cycle delay. The multiplier and adder stages require 2 clock cycles to generate their output and another clock cycle is used to sync the data with SRM2. The delay produced is constant and does not depend on the input image or filter size.

Figure 2.5: Order in which the image pixels are read

Depending on the selection signal S generated by the CSC, the role of MUX3 is to assign the appropriate set of weights to the multipliers corresponding to vertical or horizontal filter. In the more general separable filter case, such as in the case of a Gabor filter defined as  $g(x,y) = Aexp\{-(x^2+y^2)/2\sigma^2\}cos(w_ox)$ , the vertical and horizontal filter weights differ. Of course, if the filter weights for the horizontal and vertical direction are identical, MUX3 can be completely eliminated.

#### 2.4.3 Multipliers and Adder

In this design, embedded multipliers are employed using the Xilinx multiplier IP core [27]. Alternatively, LUT-based multiplication reduction methods, such as the ones discussed in the introduction section, could be employed. A total of K multipliers are required in the proposed implementation. If the kernel is not squared but rectangular of size  $(K_y \times K_x)$  with  $K_y > K_x$ , then  $K_y$  multipliers are required.

Assuming that the weights are quantized to P bits, the result of each multiplication will consist of 2P-bits. The final result obtained from the adder is scaled to ensure that the intensity value of the output pixel does not exceed P bits. This can be achieved by retaining only the P most significant bits generated by the adder.

#### 2.4.4 Central Selection Controller

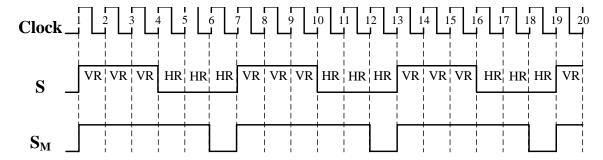

Signal S, which is generated by the CSC, is sent to MUX1, MUX2, MUX3 and DEMUX, while signal  $S_M$  is sent to memory. A counter, C, is used to set the value of signals S and  $S_M$  at each clock cycle. More specifically, S = HIGH for C = 0, ..., (K - 1), and S = LOW for C = K, ..., (2K - 1). Similarly,  $S_M = HIGH$  for C = 0, ..., (2K - 2), and  $S_M = LOW$  for C = (2K). Each window,  $W_A^{i,j}$ , consists of (2K - 1) pixels, yet (2K) clock cycles are needed to produce K convolution results. Thus, an image pixel is not read once every K clock cycles, when  $S_M = LOW$ .

The timing diagrams of signals S and  $S_M$  for a separable filter of size  $3 \times 3$  are shown in Fig. 2.6. As described in Fig. 2.6, vertical results (VR) are produced during S = HIGH. During the period when S = LOW, horizontal results (HR) are produced. At the same time,

Figure 2.6: Central selection controller timing diagram

the architecture has the opportunity to read pixels from the next window  $W_A^{i,j+1}$  or  $W_A^{i+K,j}$  and populate SRM1 with new data.

#### 2.5 Performance Analysis

The proposed technique is implemented on Xilinx Genesys Virtex 5 LX50T [28] FPGA board in VHDL language using the ISE 13.4 software. To the best of the authors' knowledge, only the FB scheme [5],[14],[15],[25] has been presented in the literature for separable convolution. In order to make additional comparisons, the authors designed a PB scheme for separable kernels, as a direct extension of the PB scheme for non-separable kernels found in [9]. The proposed scheme is compared with the FB scheme and the separable version of the PB scheme in terms of resource utilization (number of flip flops and LUT-flip flop pairs), EMB (pixels/cc) and processing rate (output pixels/cc). The non-pipelined versions of all schemes, namely FB, PB, and proposed, were implemented in this work. As a reminder, the term "non-pipelined" is used in the sense that the multipliers are reused for vertical and horizontal convolution. For all implementations, BRAM is used to store the input and output images. All images used were of size 128 × 128.

|          | External Memory       | Embedded    | <b>Processing Rate</b> |  |

|----------|-----------------------|-------------|------------------------|--|

| Method   | Bandwidth (pixels/cc) | Multipliers | (output pixels/cc)     |  |

| FB       | 0.5                   | K           | 0.5                    |  |

| PB       | $\lceil K/2 \rceil$   | K           | 0.5                    |  |

| Proposed | (2K-1)/(2K)           | K           | 0.5                    |  |

Table 2.1: Characteristics of the three schemes for a  $K \times K$  filter

The characteristics of FB, PB and proposed schemes are summarized in Table 2.1. The EMB required for the FB scheme is 1 pixel per 2 clock cycles or 0.5 pixels/cc. The upper bound of the EMB for the proposed scheme is 1 pixel/cc. Although the EMB upper bound for the proposed scheme is almost twice as large as the EMB for the FB scheme, it is still considered quite small, and it is independent of the filter kernel size. On the other hand, the PB scheme has a significantly higher EMB, which increases proportionally to the kernel size.

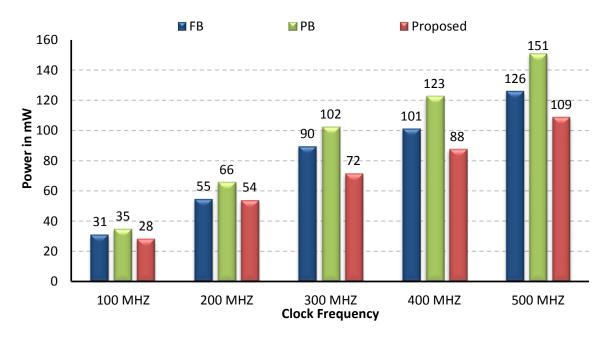

The dynamic power analysis of FB, PB, and proposed schemes is summarized in Fig. 2.7 for a kernel of size  $3 \times 3$  and clock frequencies varying from 100MHZ to 500MHZ. It is evident from Fig. 2.7 that the proposed architecture consumes less power compared to the other two architectures, especially as the clock frequency increases. The larger power consumption for FB and PB is partially attributed, respectively, to the operation of a large number of line buffers, and to the multiple pixel readings/cc.

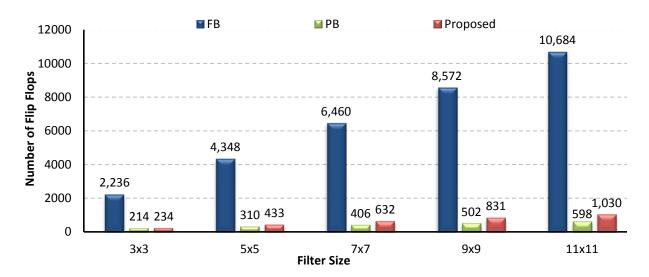

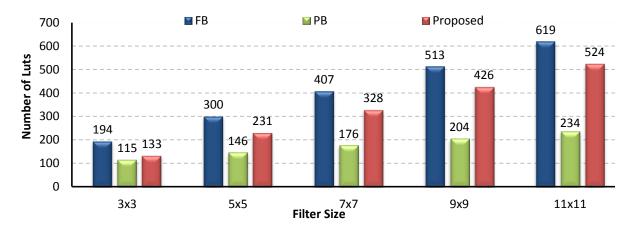

Comparisons between the three schemes in terms of flip flop count are summarized in Table 2.2 for various filter sizes. It can be observed that for smaller size filters, the flip flop utilization for the proposed scheme is only moderately larger than that of the PB scheme, and still remains significantly smaller to that of the FB scheme, even as the filter size increases. As a result, the proposed technique provides an appropriate trade off between EMB and resource utilization.

Figure 2.7: FB, PB and proposed schemes power consumption (mW) for a  $3 \times 3$  filter

| Filter Size    | FB    |     | PB  |     | Proposed |     |

|----------------|-------|-----|-----|-----|----------|-----|

| Filter Size    | FF    | LUT | FF  | LUT | FF       | LUT |

| $3 \times 3$   | 2236  | 194 | 214 | 115 | 234      | 133 |

| $5 \times 5$   | 4348  | 300 | 310 | 146 | 433      | 231 |

| $7 \times 7$   | 6460  | 407 | 406 | 176 | 632      | 328 |

| $9 \times 9$   | 8572  | 513 | 502 | 204 | 831      | 426 |

| $11 \times 11$ | 10684 | 619 | 598 | 234 | 1030     | 524 |

Table 2.2: Comparison between FB, PB and proposed schemes for various filter sizes in terms of flip flops and LUTs using xilinx virtex 5 FPGA device

Figure 2.8: Comparison between FB, PB and proposed schemes for various filter sizes in terms of flip flops shown using barplots

Figure 2.9: Comparison between FB, PB and Proposed schemes for various filter sizes in terms of LUTs shown using barplots

#### 2.6 Conclusions

A new scheme for separable convolution on FPGA was proposed. Compared to the existing schemes, the proposed technique provides a more appropriate balance between on-chip resource utilization and EMB.

For instance, although PB requires moderately fewer resources compared to the proposed scheme, this advantage is overshadowed by its high EMB requirements. External memory elements such as SDRAM or DDRAM may not be capable of transfer rates comparable to that of the system clock. For example, the DDRAM2 available on Virtex 5 LX devices has a maximum transfer rate of 600 Mb/s [29], or 75 Mpixels/s for grayscale images, while the Virtex 5 LX50T [28] system clock runs at 500MHz. According to Table 2.1, PB requires that EMB is K/2 pixels/cc for a processing rate of 0.5 output pixels/cc. To achieve the required EMB using DDRAM2, the system clock should be slowed down, resulting in a processing rate which is K/2 times slower than that of the proposed scheme.

The EMB requirements for FB allow the processing rate to be twice than that of the proposed method. However, the resource requirements for FB significantly limit its usability with large images or large filter kernels. For example, using Virtex 5 LX50T with FB and a  $11 \times 11$  filter, only images with up to 345 columns can be processed. The proposed scheme is independent of image size, therefore considerably larger filters can be implemented on Virtex 5 LX50T.

Although it is not the objective of this work, it is worth mentioning that employing LUT-based multiplier-equivalent circuits [18],[19],[20],[21],[22] may further reduce resource utilization.

#### Chapter 3

# An Efficient Method of Error Reduction in Logarithmic Multiplication for Filtering Applications

#### 3.1 Abstract

Many real-time digital signal and image processing applications demand high performance. This can be achieved at the expense of area, power dissipation and accuracy. Multiplication is one of the most critical and time consuming step in filtering applications. An alternative way is to convert multiplication to addition by converting the integer number system to the logarithmic number system. However, multiplication in logarithmic domain in not accurate. In image and signal processing applications, where filtering is most widely used, small errors introduced with multipliers do not affect the results significantly and can be used in practice. The proposed method alters the filter weights so that the error produced by multiplication in the logarithmic domain is reduced without increasing any additional circuitry or resources except the basic Mitchell-based logarithmic multiplier.

#### 3.2 Introduction

Filtering is a computationally complex process which is most widely used in image and signal processing applications. Arithmetic operations such as multiplication and division are complex in terms of area, delay, speed and power. Converting the integer number system to the logarithmic number system (LNS) will convert arithmetic operations such as multiplication to addition, division to subtraction, power to multiplication, and roots to division. However, the results obtained in LNS are not accurate. In image and signal processing applications such as image enhancement [4], smoothing [12],[5] and edge detection [2], accurate result of the multiplication is not essential and an approximate result of the multiplication is practically acceptable in most cases. Hence, LNS is a simple alternative to computing multiplication.

Mitchell [7] first proposed a simplified method for computing multiplication in LNS domain by

using a straight line approximation technique. Mitchell's method calculates the approximate logarithmic value of a number by encoding a binary number into a format from where the characteristic is determined exactly and the mantissa is calculated approximately. The logarithm and anti-logarithm functions in Mitchell's method use less hardware and no LUT is required. However, multiplication results obtained using Mitchell's method have a maximum possible relative error of around 11% and the average error is around 3.8%.

Numerous attempts have been made to improve Mitchell's approximation by proposing several error correction circuits. These methods include Mitchell-based methods [30],[31],[32],[33], LUT-based methods [34],[35],[36], and region-based approaches [37],[38],[39],[40],[41],[42].

In [7], Mitchell has shown that the relative error increases with the number of bits with the value of 1 in the mantissa. Using this idea, the operand decomposition (OD) method proposed in [30] reduces the number of 1 bits by decomposing the operands, which in turn decreases the chances of carryover from the mantissa part to the integer part during the logarithmic summation step. In [31], an implementation of 2D convolution based on the Mitchell logarithmic multiplier is presented with an aim of minimizing the power consumption. A partitioning and gating technique is proposed to reduce the switching activity based on the detection of insignificant data bits. In [32],[33], a single stage of the iterative algorithm follows the idea of Mitchell but uses a different error correction circuit which aids in increasing the accuracy and efficiency of iterative method. The final pipelined hardware of the iterative method results in reduction of logic utilization and power consumption.

An LUT-based approach to design error correction circuits for the logarithmic multiplier is proposed in [34]. This approach is faster and has a simple error correction circuit. But, this method requires large number of logic gates to implement the LUT. A hardware efficient architecture based on [34] is proposed in [35]. It uses an LUT followed by a multiplier-less linear interpolation stage. In [36], the author proposed logarithmic approximation by combining the Mitchell method with two correction stages. The first stage is a piece-wise linear interpolation with power-of-two slopes and truncated mantissas', and the next stage is an LUT-based correction that corrects the piece-wise interpolation error. Hence, LUT-based

methods are fast but inefficient in terms of hardware resource utilization which increases abruptly for inputs with large bit width.

Several region-based approaches are proposed in the literature for improving the accuracy of the results obtained using the Mitchell logarithmic multiplier. In [37] and [38], the mantissa range of [0,1) was partitioned into four parts, and a separate approximation equation was obtained by using trial and error method for each sub interval. The coefficients of each interval are chosen in such a way that numerator is integer and denominator is powers of two, where as the coefficients used in [37] are not powers of two. It has to be noted at this point that the sum operations are performed at full precision. Hence, the error while computing logarithmic process is reduced but with an increased hardware and longer computation time. In [37] and [38], both methods use all the bits of the mantissa and the coefficients are not all powers of two, which is addressed in the next methods by [39] and [40].

In [39], the author takes into consideration only the mantissas' four most significant bits (MSB) and divides the power-of-two intervals into two regions and further reduce the complexity by only using the mantissas' four MSBs. In [40] and [41], the author extends this approach by dividing the interval into two, three, and six regions and further reduces the complexity by only using the mantissas' three MSBs. The advantage of using this method is that the error correction does not need to be done on all mantissa bits. In [42], the exact logarithmic curve is divided into two symmetric regions obtaining a reduced error of 0.045. It has to be noted at this point that the coefficients derived in methods [39], [40] and [42] are restricted to the powers of two. Based on [40] and [41], a logarithmic multiplier architecture for complex numbers is proposed in [43]. Besides the region-based approach, linear programming techniques are used to obtain optimized coefficients for designing logarithmic converters [44] and anti-logarithmic converters [45].

This chapter is organised as follows: Section 3.3 discusses in more detail the Mitchell logarithmic multiplier and the iterative Mitchell (IM) multiplier. Section 3.4 discusses the proposed logarithmic multiplier. Section 3.5 presents results with comparisons between the proposed and existing logarithmic multipliers. Section 3.6 presents briefly the extension of the proposed logarithmic multiplier. Some concluding remarks are presented in section 3.7.

#### 3.3 Review of Logarithmic Multipliers

Logarithmic multiplication introduces an operand conversion from the integer number system into the LNS. The multiplication of two operands  $N_1$  and  $N_2$  is performed in three phases: calculating the operand logarithms, the addition of the operand logarithms, and the calculation of the anti-logarithm. The main advantage of this method is the substitution of the multiplication with addition after the conversion of operands to logarithms.

#### 3.3.1 Mitchell Logarithmic Multiplier

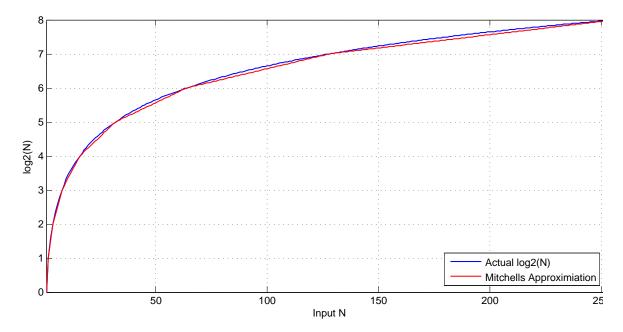

Mitchell presented a simple method to approximate the logarithm and anti-logarithm calculations using piece-wise straight line approximations of the log and anti-log curves. The approximated curve obtained from the Mitchell log approximation and the actual curve for  $log_2$  of an integer N is shown in Fig. 3.1. Mitchell's method accurately calculates the result when the number N is a perfect power-of-two numbers such as 2, 8, 16, 32, 64, 128, 256 and so on. The maximum error occurs at the mid-point between the two consecutive power-of-two numbers such as 192. The error in Mitchell's log is due to the fractional part of the log. Hence, whenever the fractional part is zero (i.e. the operand is exact power of 2), the Mitchell log curve intersects the actual log curve. In this section, derivation for multiplication of operands  $N_1$  and  $N_2$  using the Mitchell method is explained in more detail.

The binary representation of the number N can be written as given below:

$$N = \sum_{i=j}^{k} 2^i Z_i \tag{3.1}$$

Since  $Z_k$  is the MSB, we may assume  $Z_k = 1$  for any valid  $k \ge j$ . Factoring out the value of  $2^k$  from N, we get

$$N = 2^{k} \left( 1 + \sum_{i=1}^{k-1} 2^{(i-k)} Z_{i} \right) = 2^{k} (1+x)$$

(3.2)

where, k is a characteristic or the position of MSB with the value of '1',

$Z_i$  is the bit value at  $i^{th}$  position,

x is the fraction or mantissa.

Figure 3.1: Actual values and Mitchell's approximated values of  $log_2(N)$

The logarithm with the base 2 of N is derived as given below:

$$log_2(N) = log_2\left(2^k \left(1 + \sum_{i=j}^{k-1} 2^{(i-k)} Z_i\right)\right) = log_2\left(2^k (1+x)\right) = k + log_2(1+x)$$

(3.3)

Mitchell used straight line linear approximation for  $log_2(1+x)$ , which only uses the first linear term in the Taylor series:  $log_2(1+x) \approx x$ . This eliminates the need for an LUT. The approximate logarithm of the binary number using Mitchell is shown below:

$$log_2(N)_{MA} = log_2\left(2^k\left(1 + \sum_{i=j}^{k-1} 2^{i-k}Z_i\right)\right) = log_2\left(2^k(1+x)\right) = k+x$$

(3.4)

The true logarithm of this binary number is shown below:

$$\log_2(N)_{true} = k + \log_2(1+x) \tag{3.5}$$

Let  $N_1$  and  $N_2$  be the input operands. The actual logarithm of the product and approximate logarithm of the product are shown in the following two equations.

$$log_2(N_1 \times N_2)_{true} = k_1 + k_2 + log_2(1 + x_1) + log_2(1 + x_2)$$

(3.6)

$$\log_2 (N_1 \times N_2)_{MA} \approx k_1 + k_2 + x_1 + x_2 \tag{3.7}$$

The characteristic numbers  $k_1$  and  $k_2$  represent the MSBs of the operands'  $N_1$  and  $N_2$  with the value of '1'.  $x_1$  and  $x_2$  represent fractions of the operands'  $N_1$  and  $N_2$  respectively. For 16 bit numbers, the range of  $k_1$  and  $k_2$  characteristic numbers is from 0 to 15. The fractions are in the range of [0,1). The above equation 3.7 is rewritten as two separate expressions to account for the two possible cases of carry. One is the case of "no carry" from the mantissa x to the characteristic k, and the other is the case where the "carry" occurs.

$$log_2 (N_1 \times N_2)_{MA} \approx \begin{cases} k_1 + k_2 + x_1 + x_2, & x_1 + x_2 < 1\\ 1 + k_1 + k_2 + (x_1 + x_2 - 1), & x_1 + x_2 \ge 1 \end{cases}$$

(3.8)

Taking antilogarithm to the above equation 3.8 gives the final product  $P_{MA}$ .

$$P_{MA} \approx \begin{cases} 2^{k_1 + k_2} \left( 1 + x_1 + x_2 \right), & x_1 + x_2 < 1 \\ 2^{k_1 + k_2 + 1} \left( x_1 + x_2 \right), & x_1 + x_2 \ge 1 \end{cases}$$

(3.9)

The error due to Mitchell's approximation is in the range [0, 0.08639] and attains the maximum value when the fractional part of the log is equal to 0.44 (i.e. when the number is in the middle of power of 2). The maximum possible relative error for Mitchell's log multiplication is around 11% and the average error is around 3.8%. The error in Mitchell's method is always positive which can be reduced by successive multiplications, but the error correction can start only after the calculation of term  $(x_1 + x_2)$ . IM log multiplier which is based on successive multiplications is explained in more detail in the next section.

#### 3.3.2 Derivation of IM log multiplier

The logarithm approximation presented in equation 3.8 can be simplified by using the IM algorithm [32],[33], which is explained in more detail in this section. According to equation 3.2, the true product of operands  $N_1$  and  $N_2$  can be expressed as

$$P_{true} = 2^{k_1 + k_2} \left( 1 + x_1 + x_2 \right) + 2^{k_1 + k_2} \left( x_1 \times x_2 \right)$$

(3.10)

In order to simplify the approximation error, the following expression derived from equation 3.2 is given below:

$$N - 2^k = 2^k \times x \tag{3.11}$$

Using equation 3.11 in equation 3.10, the following expression is derived which is given below:

$$P_{true} = 2^{(k_1 + k_2)} + (N_1 - 2^{k_1}) \times 2^{k_2} + (N_2 - 2^{k_2}) \times 2^{k_1} + (N_1 - 2^{k_1}) \times (N_2 - 2^{k_2})$$

(3.12)

Let us assume

$$P_{approx}^{(0)} = 2^{(k_1 + k_2)} + (N_1 - 2^{k_1}) \times 2^{k_2} + (N_2 - 2^{k_2}) \times 2^{k_1}$$

(3.13)

Substituting equation 3.13 in equation 3.12, we get

$$P_{true} = P_{amrox}^{(0)} + (N_1 - 2^{k_1}) \times (N_2 - 2^{k_2})$$

(3.14)

If we discard the term  $(N_1 - 2^{k_1}) \times (N_2 - 2^{k_2})$  from equation 3.14, we have approximate product of the operands  $N_1$  and  $N_2$ . The error term  $(N_1 - 2^{k_1}) \times (N_2 - 2^{k_2})$  can be calculated in the similar manner as  $P_{approx}^{(0)}$  until  $P_{approx}^{(0)}$  is equal to  $P_{true}$ . Hence, the comparison of the addend  $(x_1 + x_2)$  is completely eliminated, and the error correction can start immediately after removing leading ones from the operands  $N_1$  and  $N_2$ . The expression for multiplication using i correction terms is given below:

$$P_{true} = P_{approx}^{(0)} + C^1 + C^2 + \dots + C^i = P_{approx} + \sum_{j=1}^{i} C^j$$

(3.15)

The number of iterations required for obtaining results with zero error is equal to the number of bits with the value of '1' in the operand. Moreover, the operand which has smaller numbers of bits with the value of '1' is taken into consideration for calculating the number of iterations.

### 3.4 Proposed logarithmic multiplier

For filtering applications, the filter weights are already known and fixed. Taking this into account, the proposed method modifies the given weights so that the product error is reduced. The derivation for calculating optimized weights for the proposed method is described below:

Let  $N_1$  be the image pixel and  $N_2$  be the filter weight. Similar to the representation in equation 3.2,  $N_1$  can be expressed as given below:

$$N_1 = 2^n + (N_1 2^{-n} - 1)2^{-n} (3.16)$$

Applying log 2 on both sides of equation 3.16 we get,

$$log_2(N_1) = n + (N_1 2^{-n} - 1) (3.17)$$

Here it is assumed that  $log_2((N_12^{-n}-1)2^{-n})\approx N_12^{-n}-1$ . Similarly applying  $log_2$  on the filter weight  $N_2$  we get,

$$log_2(N_2) = W_I + W_F (3.18)$$

where,  $W_I$  is the integer part of the weight  $N_2$ , and

$W_F$  is the fractional part of the weight  $N_2$ .

The product of  $N_1$  and  $N_2$  in LNS domain can be derived as

$$log_2(N_1 \times N_2) = \left[ n + (N_1 2^{-n} - 1) \right] + \left[ W_I + W_F \right]$$

(3.19)

By rearranging the above equation and taking into consideration the cases of "no carry" and "carry", the following equations are derived respectively.

$$log_{2}(N_{1} \times N_{2}) \approx \begin{cases} [n + W_{I}] + [(N_{1}2^{-n} - 1) + W_{F}], & (N_{1}2^{-n} - 1) + W_{F} < 1\\ [n + W_{I} + 1] + [(N_{1}2^{-n} - 2) + W_{F}], & (N_{1}2^{-n} - 1) + W_{F} > 1 \end{cases}$$

(3.20)

Applying antilog on both sides of the equation 3.20, we get

$$(N_1 \times N_2) \approx \begin{cases} 2^{W_I} N_1 + 2^{(n+W_I)} W_F, & (N_1 2^{-n} - 1) + W_F < 1 \\ 2^{W_I + 1} N_1 + 2^{(n+W_I + 1)} (W_F - 1), & (N_1 2^{-n} - 1) + W_F > 1 \end{cases}$$

(3.21)

Applying mean square error (MSE) to equation 3.21 w.r.t product of original operands  $N_1$  and  $N_2$  and equating it to zero, the following expression is derived:

$$\sum_{N_1} \left[ N_1 2^{W_I} + W_F 2^{(n_1 + W_I)} - N_1 N_2 \right]^2 + \sum_{N_2} \left[ N_2 2^{(W_I + 1)} + (W_F - 1) 2^{(n_2 + W_I + 1)} - N_1 N_2 \right]^2 = 0$$

(3.22)

Now differentiating the above equation 3.22 w.r.t fractional part of the filter weight  $W_F$ , we get

$$W_F = \frac{\sum_{N_1} N_1 2^{n_1} \left( N_2 - 2^{W_I} \right) + \sum_{N_2} N_2 2^{(n_2+1)} \left( N_2 - 2^{W_I+1} \right) + \sum_{N_2} 2^{(2n_2+W_I+2)}}{\sum_{N_1} 2^{(2n_1+W_I)} + \sum_{N_2} 2^{(2n_2+W_I+2)}}$$

(3.23)

### 3.5 Results and Discussion

The fractional part of the original filter weight is modified and replaced by the value obtained using the equation 3.23. This value ensures the reduction of error in multiplying  $N_1$  and  $N_2$ . The proposed method, Mitchell method, OD method, and IM method with 2 and 3 stages are implemented in Matlab, and the average relative error is calculated to evaluate accuracy of the proposed algorithm.

The average relative error is calculated as follows:

$$AverageErrorPercentage = \sum_{i=1}^{N} \frac{EP_i}{N}$$

(3.24)

where,  $ErrorPercentage = \left\lceil \frac{TV - LV}{TV} \right\rceil \times 100;$

TV is the true value obtained using binary multiplication,

LV is the value obtained using the above proposed logarithmic multipliers,

N is the total number of multiplications performed.

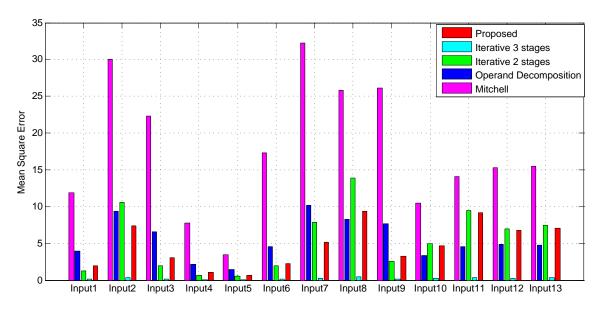

For instance, if the input operands  $N_1$  and  $N_2$  are represented using 8 bit numbers, then all the combination of numbers ranging from 1 to 256 are multiplied, and the average error percentage is calculated. The average error percentage reported for the Mitchell algorithm in [7] is 3.87%, OD in [30] is between 2.07% and 2.15%, and the IM algorithm with 2 stages is between 0.83% and 0.99%. The average error percentage for the proposed logarithmic multiplier is around 0.1%.

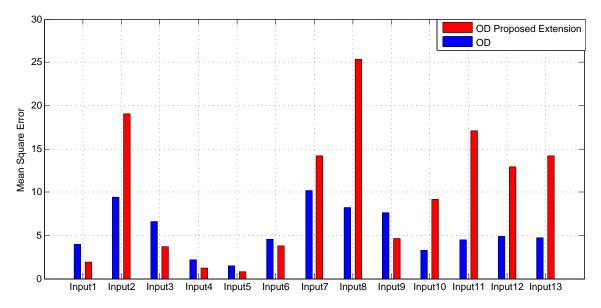

MSE's of all the above methods are calculated and tabulated in Table 3.1. Fig. 3.2 depicts the MSE's of all the above methods using barplots. It is evident from Table 3.1 and Fig. 3.2 that, logarithmic multiplication of operands  $N_1$  and  $N_2$  using the proposed method produces less error when compared to the Mitchell, OD, and IM algorithm with 2 stages. The IM algorithm with 3 stages produces the least error of all the methods but at a cost of much increased resource utilization. The objective of the proposed logarithmic multiplier is to reduce the product error without any increase in the circuit of the basic Mitchell multiplier. In section 3.6, the proposed method for logarithmic multiplication is extended where the error can be further reduced with little increase in the circuit of the basic Mitchell multiplier. It is worth

| Input<br>Signal | Mitchell | OD    | IM<br>2 stages | IM<br>3 stages | Proposed |

|-----------------|----------|-------|----------------|----------------|----------|

| Input1          | 11.84    | 4     | 1.27           | 0.1            | 1.97     |

| Input2          | 30       | 9.38  | 10.54          | 0.36           | 7.36     |

| Input3          | 22.28    | 6.62  | 1.98           | 0.13           | 3.07     |

| Input4          | 7.79     | 2.14  | 0.68           | 0.04           | 1.1      |

| Input5          | 3.44     | 1.47  | 0.51           | 0.05           | 0.61     |

| Input6          | 17.32    | 4.59  | 1.96           | 0.12           | 2.23     |

| Input7          | 32.22    | 10.22 | 7.82           | 0.3            | 5.2      |

| Input8          | 25.87    | 8.24  | 13.85          | 0.41           | 9.42     |

| Input9          | 26.16    | 7.63  | 2.54           | 0.16           | 3.28     |

| Input10         | 10.52    | 3.32  | 4.99           | 0.22           | 4.67     |

| Input11         | 14.07    | 4.52  | 9.48           | 0.35           | 9.18     |

| Input12         | 15.33    | 4.88  | 6.97           | 0.27           | 6.8      |

| Input13         | 15.52    | 4.77  | 7.43           | 0.31           | 7.04     |

Table 3.1: MSE between the Mitchell, OD, IM and proposed methods using input signals of size  $1\times256$  and Gaussian filter of size  $1\times13$

mentioning at this point that the proposed method doesn't require any extra circuitry for hardware implementation, since the original filter weights are replaced by the modified weights. Hence,

Figure 3.2: MSE between the Mitchell, OD, IM and proposed methods using input signals of size  $1 \times 256$  and Gaussian filter of size  $1 \times 13$ , shown with barplots

the proposed method can be implemented on FPGA without any increase in the circuitry of the basic Mitchell multiplier, but it still provides accurate results. The authors in [32] implemented 16 bit logarithmic multipliers on the Xilinx xc3s1500-5fg676 FPGA [46] using the Mitchell method, OD method and the IM method with 1, 2 and 3 stages. The resource utilization for the non-pipelined implementation of 16 bit logarithmic multiplier as reported in [32] is compared with the proposed method. Table 3.2 presents the comparison of the above mentioned methods in terms of LUTs, slices, flip flops, and input/output blocks (IOBs).

| Logarithmic Multiplier | LUTs | Slices | Slice FFs | IOBs |

|------------------------|------|--------|-----------|------|

| Mitchell               | 622  | 321    | 66        | 99   |

| OD                     | 1187 | 604    | 101       | 99   |

| IM 1 stage             | 533  | 276    | 64        | 99   |

| IM 2 stages            | 1099 | 564    | 80        | 99   |

| IM 3 stages            | 1596 | 814    | 77        | 99   |

| IM 4 stages            | 1937 | 993    | 78        | 99   |

| Proposed               | 622  | 321    | 66        | 99   |

Table 3.2: Resource utilization of non-pipelined logarithmic multiplier using the Mitchell, OD, IM (1, 2, 3 and 4 stages), and proposed method

### 3.6 Extension of Proposed Logarithmic Multiplier

In this section, the proposed method is extended, based on the Mitchell algorithm where the error is further reduced, with little increase in circuitry of the basic Mitchell logarithmic multiplier. Instead of storing the filter integer values, storing the true log2 value of filter weights reduces the error of the product result. Based on this observation, all the above mentioned algorithms are implemented by storing true log2 value of the second operand, i.e.  $N_2$ .

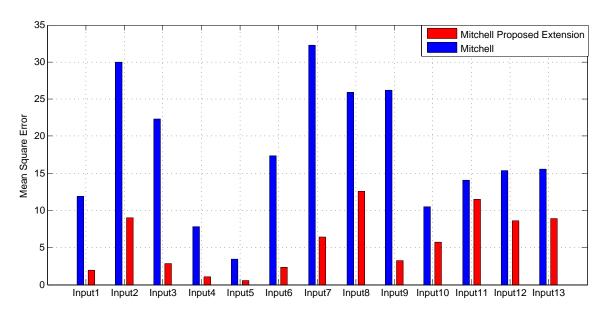

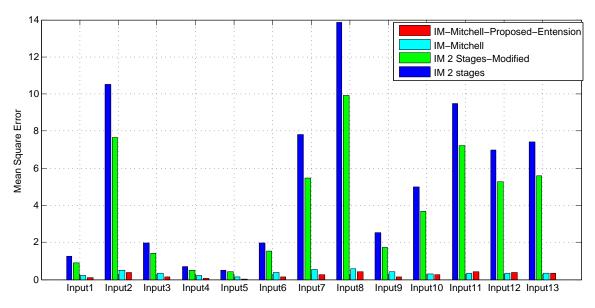

A comparison of existing methods (Mitchell, OD and IM) with the proposed method extension is performed, and the MSE's are calculated for each method. Table 3.3, Fig. 3.3, Fig. 3.4 provides a comparison between the Mitchell, proposed method extension for Mitchell, OD, and proposed method extension for OD in terms of MSE for input signals of size  $1 \times 256$  and Gaussian filter of size  $1 \times 13$ . From Fig. 3.3, it is evident that the proposed method extension for Mitchell reduces the product error significantly without any additional utilization of resources. This is achieved by storing true log2 value of the filter (i.e.  $N_2$ ), instead of storing the original number. Similarly, from Fig. 3.4, the proposed method extension for OD is not feasible and does not provide an accurate product when compared to the original OD method. Moreover, the proposed method extension for OD requires a storage of true log2 values of all the decomposed operands which increases the memory and resource utilization. Hence, the extension of the proposed method is not applicable for the OD method.

In the IM method, the first stage is similar to the Mitchell algorithm and the second stage involves the error correction circuit. From our analysis and implementation, the product error can be reduced significantly when both the first and second stages of the IM method are implemented using the proposed method extension for Mitchell. Table 3.4 and Fig. 3.5 provides the comparison between IM and the proposed method extension for IM in terms of MSE using input signals of size  $1 \times 256$  and Gaussian filter of size  $1 \times 13$ . In Table 3.4 and Fig. 3.5, the column headed "IM 2 stages" represents direct implementation of the IM method with 2 stages. The column headed "IM 2 stages-Modified" represents implementation of the IM method with 2 stages where true log2 value of the operands is taken into consideration. The column headed "IM-Mitchell" represents implementation of the IM 2 stages using the original Mitchell

| Input           |          | Mitchell  |       | OD        |

|-----------------|----------|-----------|-------|-----------|

| Input<br>Signal | Mitchell | Proposed  | OD    | Proposed  |

| Signai          |          | Extension |       | Extension |

| Input1          | 11.84    | 1.95      | 4.00  | 1.91      |

| Input2          | 30.00    | 8.96      | 9.38  | 19.07     |

| Input3          | 22.28    | 2.82      | 6.62  | 3.74      |

| Input4          | 7.79     | 1.07      | 2.14  | 1.26      |

| Input5          | 3.44     | 0.56      | 1.47  | 0.80      |

| Input6          | 17.32    | 2.35      | 4.59  | 3.78      |

| Input7          | 32.22    | 6.42      | 10.22 | 14.15     |

| Input8          | 25.87    | 12.59     | 8.24  | 25.38     |

| Input9          | 26.16    | 3.27      | 7.63  | 4.63      |

| Input10         | 10.52    | 5.71      | 3.32  | 9.15      |

| Input11         | 14.07    | 11.51     | 4.52  | 17.05     |

| Input12         | 15.33    | 8.55      | 4.88  | 12.89     |

| Input13         | 15.52    | 8.94      | 4.77  | 14.23     |

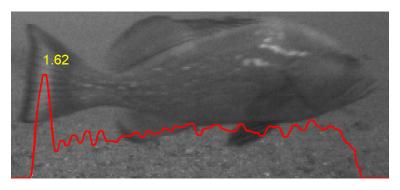

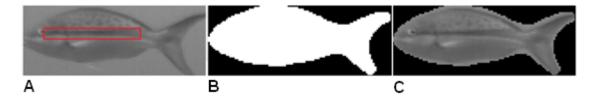

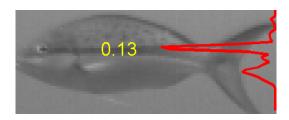

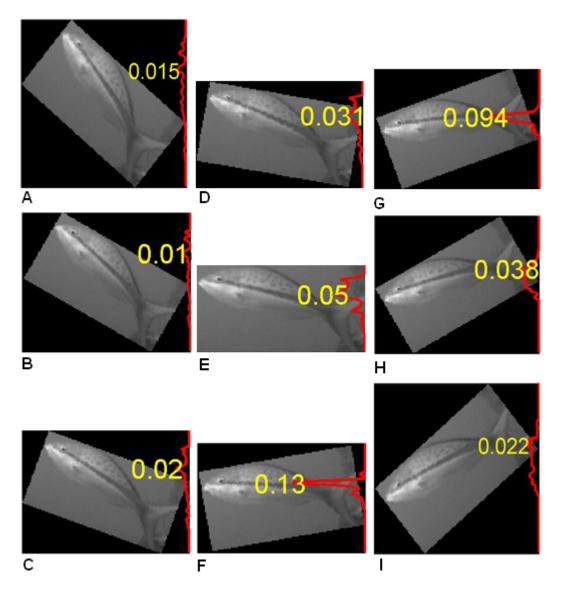

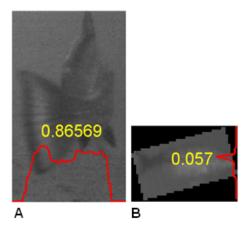

Table 3.3: MSE between the Mitchell, proposed method extension for Mitchell, OD, and proposed method extension for OD using input signals of size  $1\times256$  and Gaussian filter of size  $1\times13$